Mimas PC-FPGA interface with Wishbone master

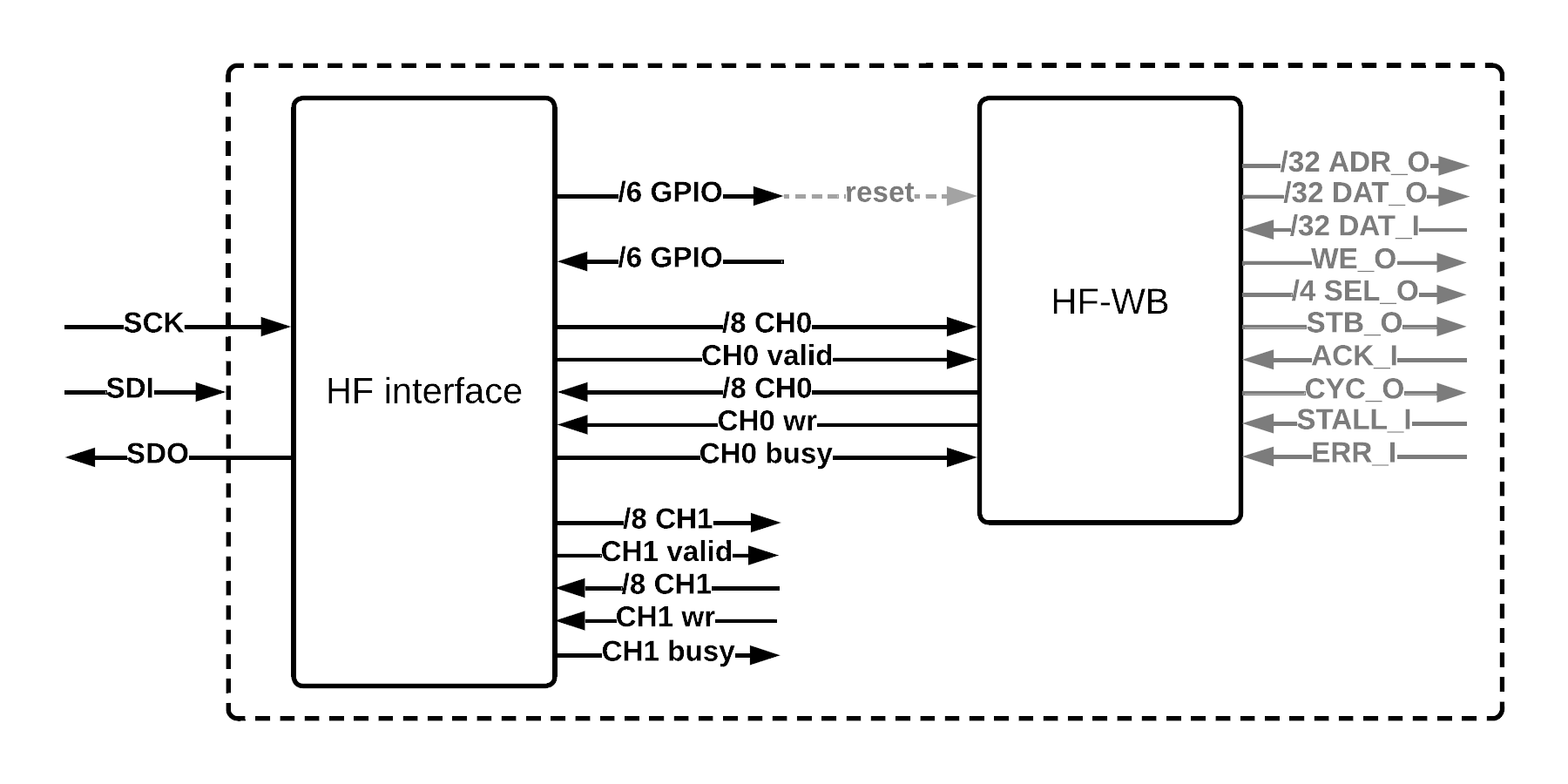

With the created PC-FPGA interface for the Mimas Spartan 6 development board, it was time to do something useful with it. I decided to make a Wishbone (version 4 pipelined) bus master which is controlled by the USB interface. This “Hardware-Firmware (HF) to Wishbone” interface can be connected to one of the HF interface channels and uses one transfer (one byte) for communicating a command and a multiple of four transfers (four bytes) for address and data transfers.

|

|---|

| System layout |

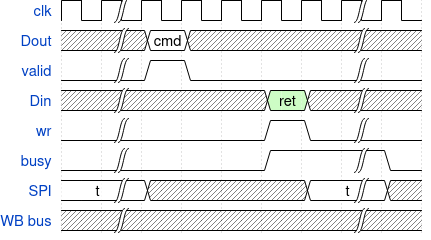

Bus Reset

The first command is the reset command (CMD=0x00) which brings the wishbone bus state back to idle. The issuer must wait for the first valid transaction on that channel and check if a valid response code is transfered (A0, an error is indicated with return code AF).

|

|---|

| HF side of bus reset |

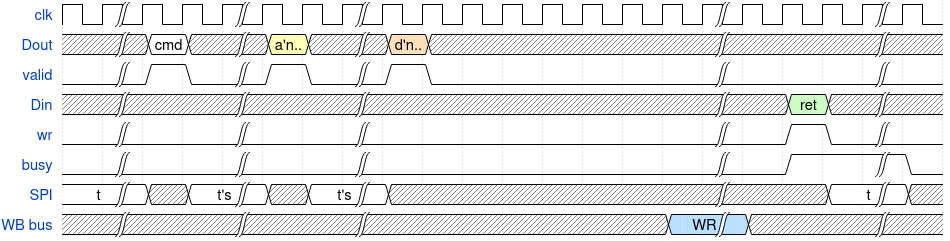

Bus Write

The second command is the write command (CMD=0x01) which requires an address and data word. After the transfers of the address and data bytes, the wishbone write transaction is activated. The issuer must wait for the first valid transaction on that channel and check if a valid response code is transferred (A0, an error is indicated with return code AF).

|

|---|

| HF side of bus write |

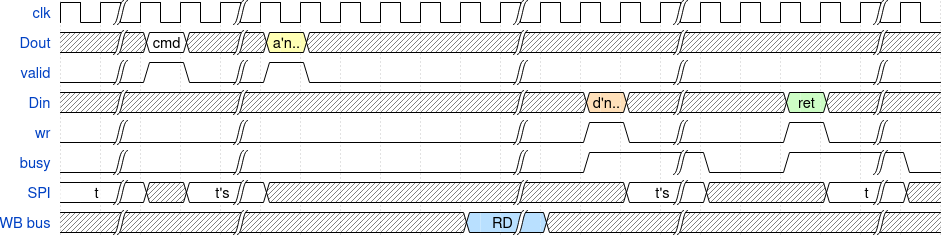

Bus Read

The third command is the read command (CMD=0x02) which requires an address. After the transfers of the address bytes, the wishbone read transaction is activated. The issuer must wait for the first valid transaction on that channel and read in 4 subsequent bytes which will contain the read-back data. Then the issuer must read one last transaction and check if a valid response code is transferred (A0, an error is indicated with return code AF).

|

|---|

| HF side of bus read |